WILEY-VCH

Alexis De Vos

# Reversible Computing

Fundamentals, Quantum Computing, and Applications

Alexis De Vos

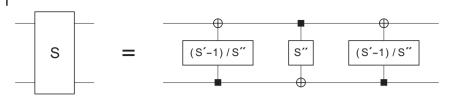

**Reversible Computing**

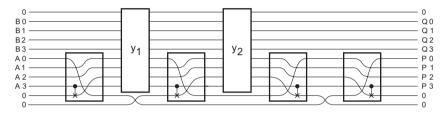

# **Related Titles**

Weidemüller, M., Zimmermann, C. (eds.)

# **Cold Atoms and Molecules**

Concepts, Experiments and Applications to Fundamental Physics

2009 ISBN: 978-3-527-40750-7

Wolf, E. L.

# Quantum Nanoelectronics An Introduction to Electronic Nanotechnology and Quantum Computing

2009 ISBN: 978-3-527-40749-1

# Morsch, O.

# **Quantum Bits and Quantum Secrets**

How Quantum Physics is Revolutionizing Codes and Computers

2008 ISBN: 978-3-527-40710-1

# Stolze, J., Suter, D.

# Quantum Computing A Short Course from Theory to Experiment

2008 ISBN: 978-3-527-40787-3

Imre, S., Balazs, F.

# Quantum Computing and Communications An Engineering Approach

2004 ISBN: 978-0-470-86902-4 Alexis De Vos

# **Reversible Computing**

Fundamentals, Quantum Computing, and Applications

WILEY-VCH Verlag GmbH & Co. KGaA

#### The Author

#### Prof. Dr. Alexis De Vos

Universiteit Gent elektronika en informatiesystemen Sint Pietersnieuwstraat 41 9000 Gent Belgium All books published by Wiley-VCH are carefully produced. Nevertheless, authors, editors, and publisher do not warrant the information contained in these books, including this book, to be free of errors. Readers are advised to keep in mind that statements, data, illustrations, procedural details or other items may inadvertently be inaccurate.

#### Library of Congress Card No.: applied for

**British Library Cataloguing-in-Publication Data:** A catalogue record for this book is available from the British Library.

# Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available on the Internet at http://dnb.d-nb.de.

© 2010 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim

All rights reserved (including those of translation into other languages). No part of this book may be reproduced in any form – by photoprinting, microfilm, or any other means – nor transmitted or translated into a machine language without written permission from the publishers. Registered names, trademarks, etc. used in this book, even when not specifically marked as such, are not to be considered unprotected by law.

Typesettingle-tex publishing services GmbH,LeipzigPrinting and BindingFabulous PrintersPte Ltd, SingaporeCover DesignFormgeber, Eppelheim

Printed in Singapore Printed on acid-free paper

ISBN 978-3-527-40992-1

# Contents

Preface IX

Introduction 1

#### **1 Boolean Algebra** 5

- 1.1 Boolean Functions of One Variable 5

- 1.2 Boolean Functions of Two Variables 6

V

- 1.3 Boolean Functions of *n* Variables 8

- 1.3.1 The Minterm Expansion 9

- 1.3.2 The Maxterm Expansion 9

- 1.3.3 The Reed–Muller Expansion 10

- 1.3.4 The Minimal ESOP Expansion 11

- 1.4 Linear Functions 11

- 1.5 Affine Linear Functions 12

- 1.6 Monotonic Functions 13

- 1.7 Boolean Derivative 13

- 1.8 Boolean Decompositions 14

- 1.9 Exercises for Chapter 1 15

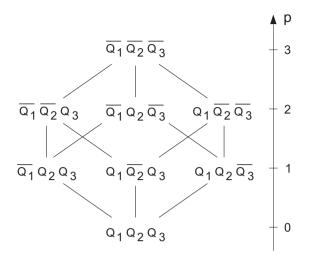

# 2 Group Theory 17

- 2.1 Introduction 17

- 2.2 Permutation Groups 19

- 2.3 Matrix Groups 21

- 2.4 Group Generators 22

- 2.5 Subgroups 23

- 2.6 Young Subgroups 23

- 2.7 Sylow *p*-Subgroups 24

- 2.8 Cyclic Subgroups 25

- 2.9 Closing Remarks 25

- 2.10 Exercises for Chapter 2 26

- **3 Reversible Computing** 29

- 3.1 Introduction 29

- 3.2 Reversible Circuits 32

- 3.3 Conservative Circuits 33

- VI Contents

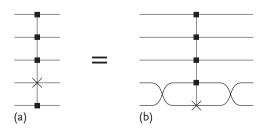

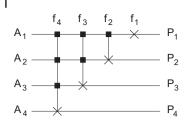

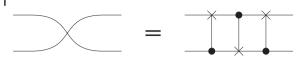

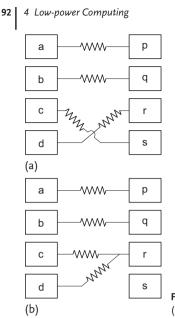

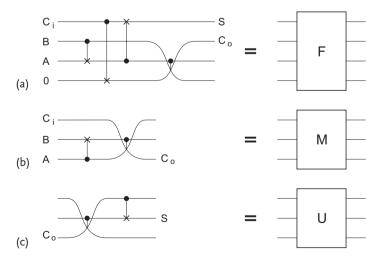

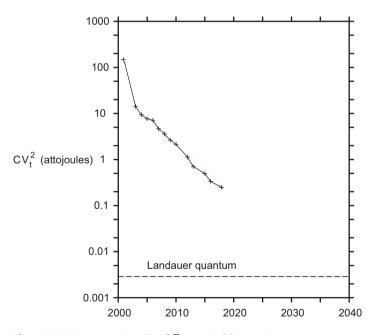

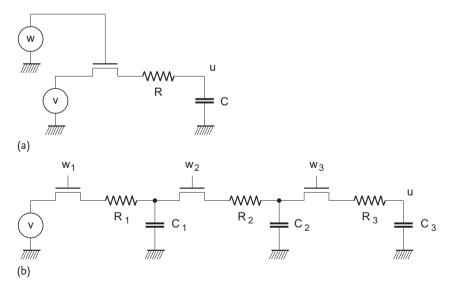

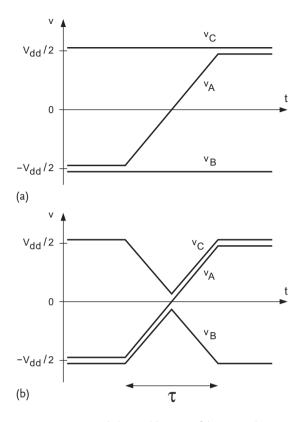

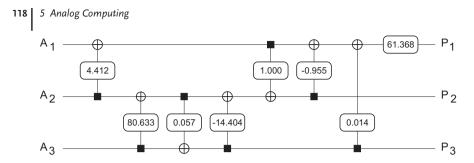

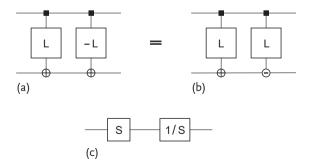

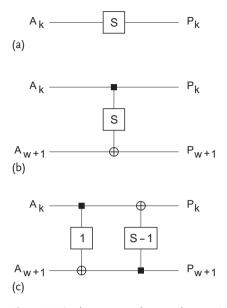

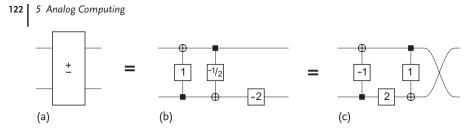

- 3.4 Monotonic Circuits 34 3.5 Linear Circuits 34 3.6 Affine Linear Circuits 36 3.7 Exchange Gates 37 3.8 SWAP Gates 39 3.9 Affine Exchange Gates 39 3.10 Control Gates 42 3.11 Sylow Circuits 47 3.12 Gate Cost and Logic Depth 49 3.13 Methods of Synthesis 51 3.14 Cosets 52 3.15 Double Cosets 55 3.16 The Synthesis Algorithm 57 3.16.1 Basic Idea of the Algorithm 58 3.16.2 Working Out the Algorithm 60 3.16.3 Results 61 3.17 Variable Ordering 64 3.18 Templates 65 3.19 The Linear Synthesis Algorithm 69 3.20 Preset Bits and Garbage Bits 72 3.20.1 Duplicating Circuit 72 3.20.2 Controlled NOT 73 3.20.3 An Application: the Majority Circuit 3.21 Another Application: the Full Adder 3.22 Avoiding Garbage 80 3.23 Exercises for Chapter 3 82 4 Low-power Computing 85 4.1 Entropy 85 4.2 Permutation Matrices 88 4.3 Landauer's Theorem 89 4.4 Thermodynamics 90 4.5 An Application: Prototype Chips 93 4.6 Switch Cost 101 4.7 Moore's Law 103 4.8 Quasi-adiabatic Addressing 105 4.9 Exercises for Chapter 4 110 5 Analog Computing 113 5.1 Computing with Real Numbers 113 5.2 Synthesis 115 5.3 An Application: the Color Transform 117 5.4 About Determinants 119 5.5 LIFT Gates versus SCALE Gates 120 5.6 Conclusion 122 5.7 Computations with Complex Numbers 123

74

77

- 5.8 An Application: the Fourier Transform 124

- 5.9 Nonlinear Computations 126

- 5.10 Exercises for Chapter 5 130

# 6 Computing in Modulo 2<sup>b</sup> 131

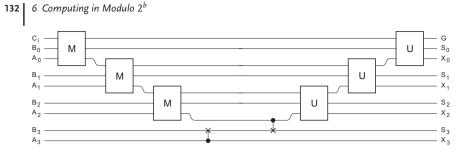

- 6.1 Addition in Modulo  $2^b$  131

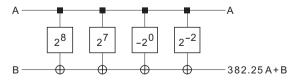

- 6.2 Multiplication by a Constant 135

- 6.3 Scaling by -1 *136*

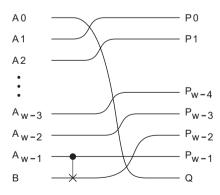

- 6.4 Scaling by 1/2 or by 2 *137*

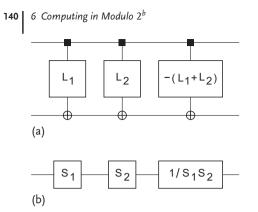

- 6.5 Lifting 139

- 6.6 Exercises for Chapter 6 141

# 7 Quantum Computing 143

- 7.1 Doubly Stochastic Matrices 143

- 7.2 Unitary Matrices 144

- 7.3 Entropy in the Quantum World 147

- 7.4 Entanglement 148

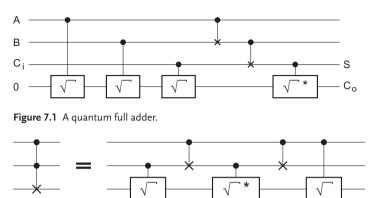

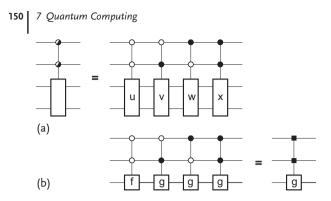

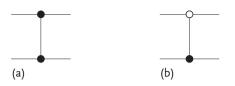

- 7.5 Control Circuits and Control Gates 149

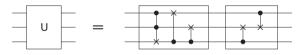

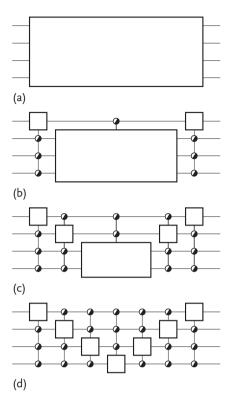

- 7.6 Synthesis 151

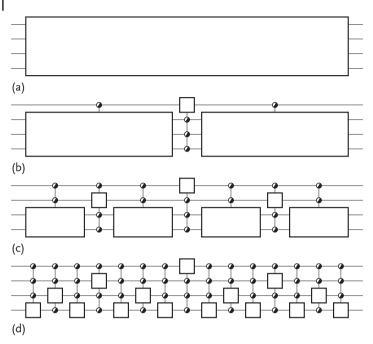

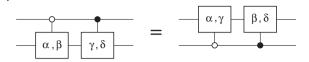

- 7.7 Decomposition 152

- 7.8 Discussion 154

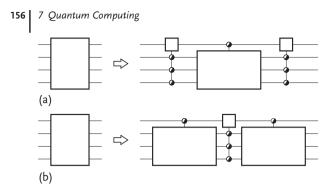

- 7.9 Bottom-Up and Top-Down 156

- 7.10 Bottom-Up Approach 157

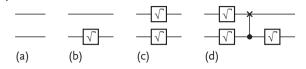

- 7.10.1 One-(Qu)bit Calculations 157

- 7.10.2 Two-(Qu)bit Calculations 159

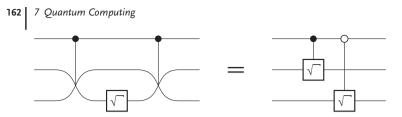

- 7.10.3 Three- and Multi-(Qu)bit Calculations 161

- 7.11 Top-Down Approach 162

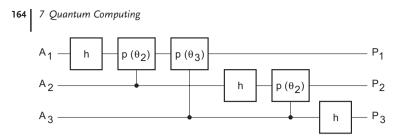

- 7.12 An Application: the Quantum Fourier Transform 163

- 7.13 Nonlinear Computations 166

- 7.14 Exercises for Chapter 7 167

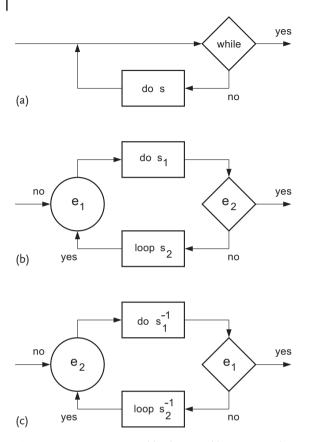

#### 8 Reversible Programming Languages 169

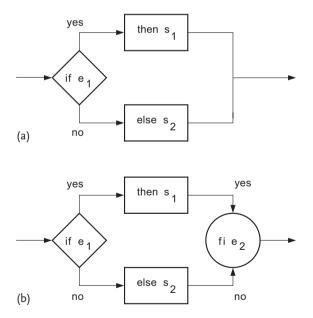

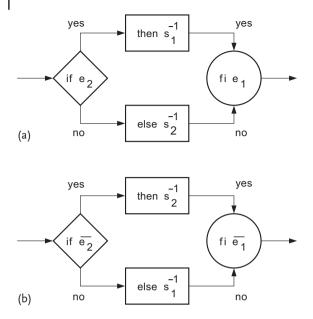

- 8.1 The if-then-else Structure 170

- 8.2 The do-until Structure 175

- 8.3 Exercises for Chapter 8 177

# Appendix A The Number of Linear Reversible Circuits 181

#### Appendix B Bounds for the q-Factorial 183

#### Appendix C A Theorem about Universal Reversible Gates 185

- C.1 Universality in Conventional Logic Circuits 185

- C.2 Preliminary Concepts 186

- C.3 No-Fan-Out Theorem and Its Consequences 187

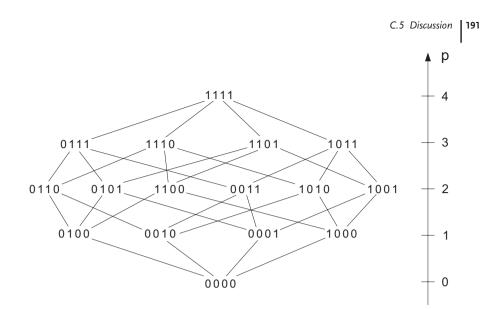

- C.4 Final Theorem 190

- C.5 Discussion 191

- C.6 Exercises for Appendix C 192

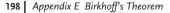

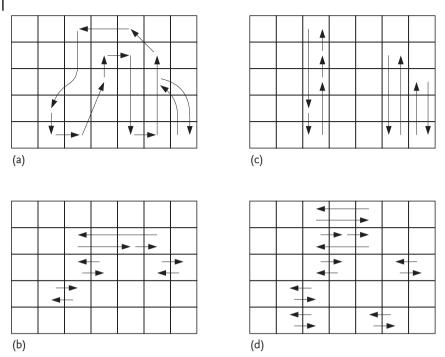

# Appendix D Synthesis Efficiency 193 Exercises for Appendix D 195 D.1 Appendix E Birkhoff's Theorem 197 E.1 Exercises for Appendix E 201 Appendix F Microentropy and Macroentropy 205 Exercises for Appendix F 207 F.1 Appendix G Computing the Successive Powers of a Matrix 209 Exercises for Appendix G 210 G.1 Post Scriptum 211 References 213 Solutions to the Exercises 223

Index 247

# Preface

The present book is dedicated to Dr. Rolf Landauer, whose early work on the subject of reversible computing inspired me to begin more than 15 years of research in this special corner of computer science. Twice I had the privilege to meet him personally: once in West Berlin (1992) and once in Boston (1996). Twice he encouraged me to continue my investigations. My research became a fascinating journey, exploring the various aspects of reversible computing. The present book aims to illustrate how the subject is interwoven with many different sections of mathematics, physics, electronics, and informatics. Reversible computers are related to low-power computing, digital electronics, analog and neural computing, quantum mechanics, as well as Boolean algebra, group theory, Lie groups and many more.

I wish to thank the three people whose support has been fruitful for many years, and without whom the book would never have been written:

- Prof. Herman Pauwels,

- Prof. Marc Vanwormhoudt,

- Prof. Andreas De Leenheer,

all three from the Universiteit Gent. I especially wish to thank people whose detailed comments, contributions and suggestions have been a continuing inspiration and encouragement:

- Prof. Leo Storme of the Universiteit Gent,

- Dr Stijn De Baerdemacker and Dr Jan De Beule of the Universiteit Gent,

- Prof. Paweł Kerntopf of the Politechnika Warszawskiego,

- Prof. Robert Glück of the Københavns Universitet, and

- Prof. Bernd Steinbach of the Bergakademie Freiberg.

The following institutions gave invaluable support:

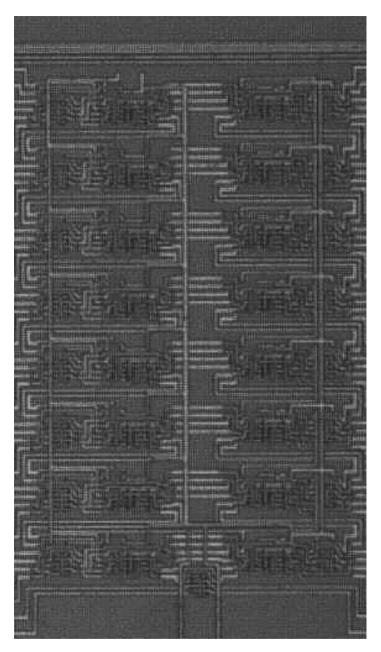

- the v.z.w. Imec (i.e., the Flemish Interuniversity Microelectronics Center), and

- the Universiteit Gent.

X Preface

In particular,

- the Invomec division of v.z.w. Imec, and

- the Eurochip and Europractice consortia

gave invaluable aid with the realization of prototype chips at *Alcatel Microelectronics* (Oudenaarde, Belgium), *Austria Mikro Systeme* (Unterpremstätten, Austria), and *AMI Semiconductor* (Oudenaarde, Belgium). Finally, the following people are thanked for their direct help with the accomplishment of the book:

- Ph.D. students Bart Desoete, Filip Beunis, and Yvan Van Rentergem for their precious scientific contributions,

- Jean Bekaert for drawing all figures (the scientific and technical diagrams as well as the artist's impressions and the cover),

- Michael Thomsen for carefully checking the text of Chapter 8, and

- the staff of Wiley-VCH Verlag for their valuable help in editing the book.

Gent, 28 June 2010

Alexis De Vos

# Introduction

We are living in a world with an ever-increasing hunger for energy. Human energy consumption continues to grow. This evolution is not without problems, such as fuel depletion, waste disposal and climate change. Therefore, huge efforts are being made to appease our hunger for energy in a manner that generates as little damage to our environment as possible. We try to harvest renewable energy sources. We try to convert one kind of energy into another as smoothly as possible. We try to transport energy as efficiently as possible. When searching for ideal equipment to do this, engineers often refer to the Carnot engine (named after the young but visionary French engineer Sadi Carnot) as the ideal standard. This engine constitutes the ideal limit of a heat engine that converts heat into work, and attains the ultimate efficiency, known as the Carnot efficiency. Such an engine, which in the real world can only be approximated by a real engine, has the peculiar property of being reversible. This means that it runs so slowly and gently, that, at any moment, we may, by an infinitesimally small intervention, decide to reverse its sense of operation. By making an infinitely small change to an external parameter, all inside velocities, revolutions, heat flows, work flows, and so on are reversed. Produced power becomes consumed power; heat engine becomes heat pump; clockwise becomes counterclockwise: forward becomes backward.

While reversible heat engines have long been conceived (and approximated in technology), this is also true of reversible chemical engines. Conventional motors are based on the internal combustion of fuel. In the combustion chamber, a chemical reaction occurs in the form of a deflagration. Once the combustion has been initiated (by either a spark or compression), little control over it is possible, and it is very difficult to stop or reverse the burning reaction. In contrast, when it is performed in a so-called fuel cell, the same chemical reaction (oxidation) occurs in a reversible way. By applying an appropriate (external) electric voltage, we can control the direction (forward or reverse) of a chemical reaction and how swiftly it occurs. In the case of an ideal fuel cell, an infinitely small change in the external voltage is sufficient to change the direction of the chemical reaction: associations between atoms become dissociations of molecules; oxidation becomes reduction. It is no surprise that fuel cells display a much higher efficiency than internal combustion engines.

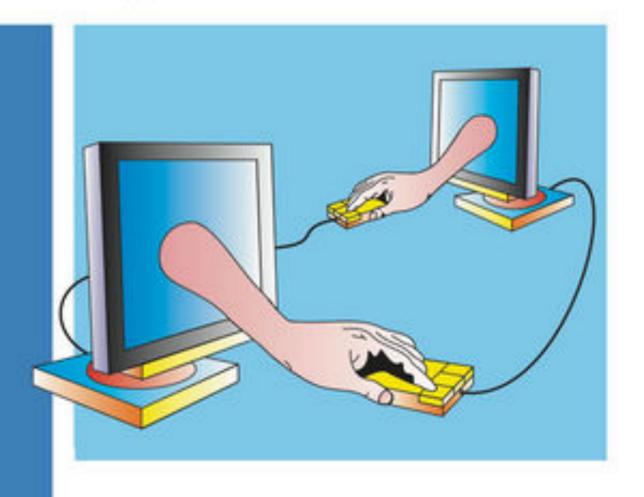

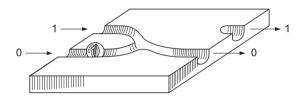

Figure 1 The simplest possible reversible computer.

Figure 2 Computation.

Besides an ever-increasing hunger for energy, our society also displays an everincreasing hunger for information. People are constantly harvesting, transporting and processing information. Little attention has been paid to the efficiency of these processes. Little effort has been expended to make these processes reversible. A loudspeaker converts electrical information into acoustic signals. For the inverse operation, we use another device: a microphone. However, the laws of physics allow the construction of devices that perform both conversions, according to an outside signal that we can influence. Current computer hardware and software are designed to perform computations in a definite direction, from input information to output information, from questions to answers. However, we can also conceive systems that can compute in either direction (forward or backward), and where the direction of computation can be chosen by the user. Indeed, at any moment (e.g., in the middle of a calculation), the user could change his or her mind and decide to alter the direction of computation. Such reversible computing models allow us to explore the fundamentals of computation, independent of any particular choice of computer hardware and computer language.

0

An example is shown in Figure 1, which depicts the simplest possible reversible computer. This is a mechanical computer that computes with one bit. It computes the inverse of an input number, which either is 0 or 1. In the former case (see Figure 2), the result is NOT(0) = 1; in the latter case, the result is NOT(1) = 0. The computation is triggered by gently raising the hand so that the bit (i.e., the marble) slowly descends from the input side (left) to the output side (right).

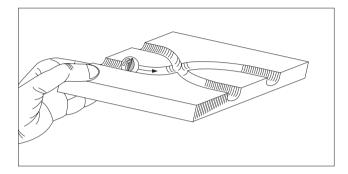

Figure 3 Decomputation.

After the marble arrives, we can change the direction of the slope in order to 'undo' the calculation and reproduce the original starting situation. Moreover, if we apply a very shallow slope, we can reverse this slope at any moment (e.g., in the middle of a computation) by exerting an infinitesimally small mechanical effort, resulting in a decomputation (see Figure 3).

Reversible energy conversion and reversible information conversion are not independent subjects. In our example, the gradient in the gravitational potential energy dictates the direction of computing. On the other hand, it is important to realize that about 10% of the world's electricity consumption is dissipated in computers. If we also consider audio and video equipment to be information processing systems, more than 20% of all electrical power is consumed in information transport and information manipulation (the rest is used for lighting, cooking, ...).

The toy computer in the above figures demonstrates that bit manipulation happens through the manipulation of physical objects. In the words of Landauer, "information is physical". There is no such thing as a 'bare' information particle (informaton). Bits piggyback on material objects (marbles, electrons, ions, photons, ...). The reversible manipulation of information and the reversible manipulation of information carriers cannot be separated. It is thus no surprise that the key to energy-efficient computing is reversible computing.

We can therefore state that the study of reversible computing leads to two benefits: on the one hand, it leads to an understanding of the basic principles; on the other hand, it leads to recipes for efficient implementations. We should not forget that Carnot's 1824 book Réflexions sur la puissance motrice du feu et sur les machines propres à développer cette puissance<sup>1)</sup> was the foundation for both a new science (thermodynamics) and a new technology (steam power).

<sup>1)</sup> Reflections on the Motive Power of Fire and on the Machines Fitted to Develop this Power.

# 1 Boolean Algebra

The vast majority of computers are digital computers; that is, computers based on a set of two numbers:  $\mathbb{B} = \{0, 1\}$ . We call the mathematics based on these two numbers Boolean algebra (named after the Irish mathematician George Boole). A Boolean variable or bit can thus take only two different values: either 0 or 1. We call  $f(A_1, A_2, \ldots, A_n)$  a Boolean function of *n* independent Boolean variables  $A_1$ ,  $A_2$ ,  $\ldots$ ,  $A_{n-1}$ , and  $A_n$ . It takes either the value 0 or the value 1, depending on the values of its arguments  $A_1, A_2, \ldots, A_n$ . This dependency is fully described using a truth table, which tells us which value *f* takes for each of the  $2^n$  different values of the (Boolean) vector  $(A_1, A_2, \ldots, A_n)$ .

In the present chapter, we will survey some properties of Boolean functions, which will allow us to gain a good understanding of binary reversible logic circuits. First, we will take a close look at Boolean functions f(A) of a single variable, then at Boolean functions  $f(A_1, A_2)$  of two variables, before we discuss Boolean functions  $f(A_1, A_2, \ldots, A_n)$  of an arbitrary number of Boolean variables. Besides recording a Boolean function unambiguously by writing down its truth table, we can also fully define a Boolean function by means of a (Boolean) formula. There are many ways to write down such a formula. We will discuss some standard ways: the minterm expansion, the maxterm expansion, the Reed–Muller expansion, and the minimal ESOP expansion. Finally, we will define a few special classes of Boolean functions; true functions and balanced functions, linear functions, affine linear functions, and monotonic functions.

## 1.1 Boolean Functions of One Variable

There are only four Boolean functions f(A) of a single Boolean variable A. Table 1.1 shows the four corresponding truth tables. However, two of these functions are not really dependent on A; they are constants:

f(A) = 0 (Table 1.1a) f(A) = 1 (Table 1.1b).

#### 6 1 Boolean Algebra

**Table 1.1** Truth table of the four Boolean functions f(A): (a) the constant function 0, (b) the constant function 1, (c) the identity function, and (d) the NOT function.

| A      | f      |    | Α      | f      |    | Α      | f      |     | A      | f      |

|--------|--------|----|--------|--------|----|--------|--------|-----|--------|--------|

| 0<br>1 | 0<br>0 |    | 0<br>1 | 1<br>1 |    | 0<br>1 | 0<br>1 |     | 0<br>1 | 1<br>0 |

| (a)    |        | (1 | D)     | 1      | (0 | c)     | 1      | (d) |        |        |

We thus have only two true functions (or proper functions) of A:

$$f(A) = A$$

(Table 1.1c)

$f(A) = \overline{A}$  (Table 1.1d)

Here, we have introduced the following shorthand notation for the inverting function or NOT function:

$\overline{X} = \operatorname{NOT} X$  .

#### 1.2

#### **Boolean Functions of Two Variables**

There are  $2^4 = 16$  different Boolean functions of two variables<sup>2</sup>). Table 1.2 shows them all. However, some of these functions f(A, B) are not actually functions of A and B; two functions are independent of both A and B. They are constants:

$$f_0(A, B) = 0$$

$f_{15}(A, B) = 1$ .

Another four functions are in fact functions of a single variable;  $f_3$  and  $f_{12}$  are independent of *B*, whereas both  $f_5$  and  $f_{10}$  are independent of *A*:

$$f_3(A, B) = A$$

$$f_5(A, B) = B$$

$$f_{10}(A, B) = \overline{B}$$

$$f_{12}(A, B) = \overline{A}$$

This leaves only 16 - 2 - 4 = 10 functions that are truely dependent on both *A* and *B*. We call them *true functions* of *A* and *B*.

2) Besides using the notation  $A_1, A_2, \ldots, A_n$  for the variables, we will also use the letters  $A, B, C, \ldots$  whenever this is more convenient.

| AB  | $ f_0 $ | $f_1$ | $f_2$ | $f_3$ | $f_4$ | $f_5$ | $f_6$ | $f_7$ | $f_8$ | $f_9$ | $f_{10}$ | $f_{11}$ | $f_{12}$ | $f_{13}$ | $f_{14}$ | $f_{15}$ |

|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------|----------|----------|----------|----------|----------|

| 0.0 | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1        | 1        | 1        | 1        | 1        | 1        |

| 01  | 0       | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0     | 0     | 0        | 0        | 1        | 1        | 1        | 1        |

| 10  | 0       | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1        | 1        | 0        | 0        | 1        | 1        |

| 11  | 0       | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0        | 1        | 0        | 1        | 0        | 1        |

**Table 1.2** Truth table of all sixteen Boolean functions  $f_i(A, B)$ .

Table 1.3 Truth tables of three basic Boolean functions: (a) the AND function, (b) the OR function, and (c) the XOR function.

| AB                   | f                | AB                       | f                | AB                       | f                |

|----------------------|------------------|--------------------------|------------------|--------------------------|------------------|

| 00<br>01<br>10<br>11 | 0<br>0<br>0<br>1 | 0 0<br>0 1<br>1 0<br>1 1 | 0<br>1<br>1<br>1 | 0 0<br>0 1<br>1 0<br>1 1 | 0<br>1<br>1<br>0 |

| (a)                  | )                | (b                       | )                | (c)                      | )                |

Three out of the ten true functions of two variables (i.e.,  $f_1$ ,  $f_7$ , and  $f_6$ ) are well known: the AND function, the OR function, and the XOR function (also known as the EXCLUSIVE OR). Table 1.3 gives the corresponding truth tables. We will use the following shorthand notations for these basic Boolean functions:

XY = X AND YX + Y = X OR Y $X \oplus Y = X \operatorname{XOR} Y$ .

The remaining 10 - 3 = 7 functions are considered a combination of the NOT, AND, OR, and XOR functions. For example,

$f_2(A, B) = A \text{ and } (\text{NOT } B) = A\overline{B}$ .

For convenience, the NOT of an AND is called a NAND, the NOT of an OR is called a NOR, and the NOT of a XOR is called a NXOR. For example,

$$f_8(A, B) = \operatorname{NOT} (A \operatorname{OR} B) = A + B = A \operatorname{NOR} B$$

.

NXOR is also called XAND, with the shorthand notation  $X \odot Y$ .

We observe that all six functions AND, OR, XOR, NAND, NOR, and NXOR are commutative:

X AND Y = Y AND X,

#### 8 1 Boolean Algebra

and there are similar identities for the other five functions. This is not the case for any function f(X, Y). For example, the function  $f_2$  is not commutative:

$$f_2(X, Y) \neq f_2(Y, X)$$

but  $f_2(X, Y) = f_4(Y, X)$ .

We end this section by stressing that there is no fundamental difference between the functions AND, OR, NAND, and NOR. They all are true functions that have either one 0 and three 1s or three 0s and one 1 in their truth tables. The functions XOR and NXOR are fundamentally different: they display two 0s and two 1s in their truth tables. This important distinction between AND, OR, NAND, and NOR on the one hand and XOR and NXOR on the other was stressed by Yokoyama *et al.* [1]. The function A XOR *B* is *injective* in its first argument, as is NXOR. This means that, for each value of *B*, the equality A XOR B = A' XOR *B* necessarily implies A = A'. The reader can easily verify that this is not the case with the AND function for example: A AND 0 = A' AND 0 does not imply A = A' (as we could have A = 0 and A' = 1). These facts will have far-reaching consequences.

#### 1.3

#### Boolean Functions of n Variables

There are  $2^{2^n}$  different Boolean functions of *n* variables. Each is represented by a truth table consisting of n + 1 columns and  $2^n$  rows. Table 1.4 gives an example for n = 3. This function is just one of the  $2^8 = 256$  possible for n = 3. Among these, only 218 are true functions of the three variables *A*, *B*, and *C*. Among the 256 functions for n = 3, seventy are so-called balanced functions; that is, functions that have an equal number of 1s and 0s in the output column. The function shown in Table 1.4 is both true and balanced.

It is important to use the expressions *true* and *balanced* carefully. For example, the function  $A\overline{B}$  is a true function of *A* and *B*, but is an untrue function of *A*, *B*,

| ABC                                               | f      |

|---------------------------------------------------|--------|

| 000                                               | 0<br>1 |

| 010                                               | 1      |

| 011<br>100                                        | 0 1    |

| $\begin{array}{c}1 \ 0 \ 1\\1 \ 1 \ 0\end{array}$ | 0<br>1 |

| 111                                               | 0      |

and *C*. It is not a balanced function of *A* and *B*, but it is a balanced function of the three variables A, B, and C. The reader may also notice the following property: all untrue functions are balanced.

A truth table can be summarized by a single Boolean formula. However, there are multiple ways to write a given table as a Boolean expression [2]. We will now discuss a few of them.

#### 131 The Minterm Expansion

Using the truth table, it is immediately possible to deduce the Boolean formula called the *minterm expansion*. For example, Table 1.4 yields:

$$f(A, B, C) = \overline{A} \,\overline{B} \,C + \overline{A} \,\overline{B} \,\overline{C} + A \,\overline{B} \,\overline{C} + A \,\overline{B} \,\overline{C} + A \,\overline{B} \,\overline{C} \,.$$

This consists of the OR of different terms. There are between 0 and  $2^n$  different terms present. Each term is called a minterm and consists of the AND of exactly *n* literals. Here a literal is a letter, either inverted or not; thus, whereas *X* is called a letter, both *X* and  $\overline{X}$  are called literals.

The algorithm for translating the truth table in the minterm expansion is straightforward: each row of the truth table with a 1 in the column furthest to the right yields one minterm. The latter consists of an AND of all input letters; an overlining is used if a 0 appears in the corresponding column, but not if a 1 appears in the corresponding column.

In the literature, such an expansion is sometimes referred to as a sum of products, because an OR resembles a sum in a way, while an AND resembles a product to some extext. The abbreviation SOP is also often used.

#### 1.3.2

#### The Maxterm Expansion

As there is no fundamental difference between OR and AND, it is no surprise that there is a function expansion that is like the minterm expansion but has the roles of OR and AND interchanged. Such an expansion is an AND of ORs, and is called a maxterm expansion. In our example (Table 1.4), we have

$$f(A, B, C) = (A + B + C)(A + \overline{B} + \overline{C})(\overline{A} + B + \overline{C})(\overline{A} + \overline{B} + \overline{C}).$$

The algorithm for translating the truth table into the maxterm expansion is completely analogous to the minterm algorithm: each row of the truth table with a 0 in the column furthest to the right yields one maxterm; the latter consists of an OR of all input letters, with a bar if a 1 appears in the corresponding column, and not if a 0 appears in the corresponding column. The maxterm expansion is an example of a POS or product of sums.

#### 1.3.3

#### The Reed–Muller Expansion

A fundamentally different expansion is obtained as follows. We apply to the minterm expansion the two identities

$$\overline{X} = 1 \oplus X$$

$$X + Y = X \oplus Y \oplus XY.$$

(1.1)

This leads to an XOR of ANDs. The result is subsequently simplified by applying the identities

$$\begin{array}{l} X \oplus X = 0 \\ 0 \oplus X = X \end{array}$$

In our example (Table 1.4), we obtain

$$f(A, B, C) = A \oplus B \oplus C \oplus AB .$$

(1.2)

A Reed-Muller expansion (named after the American mathematicians Irving Reed and David Muller) is an example of an ESOP expansion; that is, an 'EXCLUSIVE-OR sum of products'. Thus, just like the OR, the XOR function is considered a kind of sum. We note that the Reed-Muller expansion is fundamentally different from the minterm and maxterm expansions because of the *injectivity* of the XOR operation.

In many respects, a Reed–Muller expansion of a Boolean function resembles the well-known Taylor expansion of ordinary calculus. Let us assume a function *f* of the real numbers *x*, *y*, and *z*. Then, the Taylor expansion around the point (x, y, z) = (0, 0, 0) looks like

$$f(x, y, z) = c_{000} + c_{100}x + c_{010}y + c_{001}z + c_{110}xy + c_{101}xz + c_{011}yz + c_{200}x^2 + c_{020}y^2 + c_{002}z^2 + c_{111}xyz + c_{210}x^2y + \dots$$

The Reed–Muller expansion of a function f of the Boolean numbers A, B, and C looks like

$$f(A, B, C) = c_{000} \oplus c_{100}A \oplus c_{010}B \oplus c_{001}C$$

$$\oplus c_{110}AB \oplus c_{101}AC \oplus c_{011}BC \oplus c_{111}ABC.$$

There are three main differences:

- The Reed–Muller coefficients  $c_{ijk}$  can only be either 0 or 1.

- Each of the exponents *i*, *j*, and  $\overline{k}$  in the monomial (also known as the 'piterm')  $A^{i}B^{j}C^{k}$  can only be either 0 or 1; as a result:

- There are only a finite number (i.e., a maximum of 2<sup>*n*</sup>) of Reed–Muller terms.

Once again, we must stress that there is no fundamental difference between AND and OR, or between XOR and XAND. As the Reed–Muller expansion is an XOR of ANDs, there is a similar (dual) expansion that is an XAND of ORs [3, 4]. For example, expansion (1.2) can be rewritten as

$f(A, B, C) = A \odot C \odot (A + C) \odot (B + C).$

Unfortunately, such expressions are paid little attention in the literature.

We end this section by noting that (at least for n > 1), the Reed–Muller expansion of a balanced function lacks the highest-degree term  $A_1A_2...A_n$ . In other words, the Reed–Muller coefficient  $c_{11...1}$  of a balanced function is zero.

## 1.3.4 The Minimal ESOP Expansion

In the Reed–Muller expansion, NOT functions are not allowed.<sup>3)</sup> If we do allow NOT operations, the 'XOR of ANDs' expansion can be shortened. The shortest expansion (i.e., the one with the fewest literals) is called the minimal ESOP expansion.

The minimal ESOP expansion is quite different from the three above expansions (i.e., the minterm expansion, the maxterm expansion, and the Reed–Muller expansion) in two respects:

- It is not unique: two or even more minimal ESOP expansions of the same Boolean function may exist, and

- There is no straightforward algorithm for finding the minimal ESOP expansion(s) (except, of course, for an exhaustive search).

The last fact explains why minimal ESOPs are only known for Boolean functions with n = 6 or less [5, 6].

Our example function (Table 1.4) has two different minimal ESOPs:

$$f(A, B, C) = A \oplus C \oplus \overline{A}B$$

$$= B \oplus C \oplus A \overline{B}$$

Whereas the Reed–Muller expansion (1.2) needs five literals, these minimal ESOPs contain only four literals.

#### 1.4 Linear Functions

A function  $f(A_1, A_2, ..., A_n)$  is linear iff ('iff' means 'if and only if') its Reed–Muller expansion only contains terms with one letter:

$$f(A_1, A_2, \ldots, A_n) = c_1 A_1 \oplus c_2 A_2 \oplus \cdots \oplus c_n A_n .$$

3) In the present book we limit ourselves to so-called 'positive-polarity Reed–Muller expansions'. We thus ignore 'negative-polarity Reed–Muller expansions' and 'mixed-polarity Reed–Muller expansions' [2]. **12** 1 Boolean Algebra

| ABC                                                           | f                               | ABC                                                           | f                               | ABC                                                           | f                                    |

|---------------------------------------------------------------|---------------------------------|---------------------------------------------------------------|---------------------------------|---------------------------------------------------------------|--------------------------------------|

| 0 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 | 0<br>1<br>0<br>1<br>1<br>0<br>1 | 0 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 | 1<br>1<br>0<br>0<br>0<br>0<br>1 | 0 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 | 0<br>1<br>0<br>1<br>1<br>1<br>1<br>1 |

| 111                                                           | 0                               | 111                                                           | 1                               | 111                                                           | 1                                    |

| (a)                                                           |                                 | (b)                                                           |                                 | (c)                                                           |                                      |

Table 1.5

Truth tables for (a) a linear function, (b) an affine linear function, and (c) a monotonic function.

Because each of the *n* Reed–Muller coefficients  $c_j$  can take one of two values  $(c_j \in \{0, 1\})$ , the reader can easily verify that there are  $2^n$  different linear functions with *n* arguments. It is clear that the function defined by Table 1.4 is not linear: its Reed–Muller expansion (1.2) contains a second-degree term *AB*. In contrast, the function defined by Table 1.5a is linear, as it equals  $A \oplus C$ .

# 1.5 Affine Linear Functions

A function  $f(A_1, A_2, ..., A_n)$  is affine linear<sup>4</sup> iff its Reed–Muller expansion contains only terms with either zero or one letter:

$$f(A_1, A_2, \ldots, A_n) = c_0 \oplus c_1 A_1 \oplus c_2 A_2 \oplus \cdots \oplus c_n A_n .$$

Because each of the n + 1 Reed–Muller coefficients  $c_j$  can take one of two values, there are  $2^{n+1}$  different affine linear functions of n arguments. Among these,  $2^n$  are linear. The function defined by Table 1.5b is an example of an affine linear function, as it equals  $1 \oplus A \oplus B$ .

<sup>4)</sup> There seems to be some confusion about the meaning of the word 'linear'. Let us consider the ordinary functions f(x) of a real variable x. Sometimes all of the functions f(x) = ax + b are said to be 'linear'; sometimes only the functions f(x) = ax are considered 'linear'. In the present book, we follow the latter convention, so that the functions ax + b are said to be 'affine linear'.

#### 1.6 Monotonic Functions

We consider a function of *n* binary variables  $A_i$ . We use the different values of the vector  $(A_1, A_2, ..., A_n)$  as the coordinates of an *n*-dimensional hypercube. We can represent a Boolean function by giving each corner of the hypercube a label  $f(A_1, A_2, ..., A_n)$ . We call a path that travels from the point (0, 0, ..., 0) to the point (1, 1, ..., 1) via consecutive steps that each increase a single coordinate  $A_i$  from 0 to 1 a *climbing path*. Such a path necessarily contains *n* steps, with each being an edge of the hypercube. Note that:

- There are *n* possible choices for the first step,

- There are *n* − 1 possible choices for the second step,

- ...

- There are *n* − *j* + 1 possible choices for the *j*th step.

This means that there are *n*! different climbing paths.

A Boolean function  $f(A_1, A_2, ..., A_n)$  is *monotonic* (or monotone or unate) iff its value increases along each climbing path:  $f(A'_1, A'_2, ..., A'_n) \ge f(A''_1, A''_2, ..., A''_n)$  as soon as  $A'_i \ge A''_i$  for all *i* satisfying  $1 \le i \le n$ . There is no closed formula for the number of monotonic functions [7]. Neither Table 1.4 nor Table 1.5a nor Table 1.5b is a truth table of a monotonic function. Indeed, for each of these three functions, vertex (0, 0, 1) of the hypercube has a label of 1, whereas vertex (1, 0, 1) of the hypercube has a label of 0, such that *f* does not increase along the climbing path (0, 0, 0)–(0, 0, 1)–(1, 0, 1)–(1, 1, 1). In contrast, the function defined by Table 1.5c is monotonic.

#### 1.7 Boolean Derivative

Besides Boolean algebra, there is also Boolean calculus, which describes time-dependencies for example. At this point, it is sufficient to mention the three so-called subfunctions of a Boolean function  $f(A_1, A_2, ..., A_{j-1}, A_j, A_{j+1}, ..., A_n)$ :

$$f'(A_1, A_2, \dots, A_{j-1}, A_j, A_{j+1}, \dots, A_n) = f(A_1, A_2, \dots, A_{j-1}, 0, A_{j+1}, \dots, A_n)$$

$$f''(A_1, A_2, \dots, A_{j-1}, A_j, A_{j+1}, \dots, A_n) = f(A_1, A_2, \dots, A_{j-1}, 1, A_{j+1}, \dots, A_n)$$

$$f'''(A_1, A_2, \dots, A_{j-1}, A_j, A_{j+1}, \dots, A_n) = f' \oplus f''.$$

All three functions are independent of  $A_j$ , and are thus untrue functions of  $A_1, A_2, \ldots, A_n$ . Sometimes [8, 9] f''' is called the partial derivative of f with respect to  $A_j$ , and it is then denoted  $\frac{\partial f}{\partial A_j}$ . The reason for this name may be made

14 1 Boolean Algebra

**Table 1.6** Truth tables of the three subfunctions f', f'', and f''' of the function f(A, B, C) of Table 1.4.

| BC                   | f'               | BC                       | f''              |   | BC                       | <i>f'''</i>      |

|----------------------|------------------|--------------------------|------------------|---|--------------------------|------------------|

| 00<br>01<br>10<br>11 | 0<br>1<br>1<br>0 | 0 0<br>0 1<br>1 0<br>1 1 | 1<br>0<br>1<br>0 |   | 0 0<br>0 1<br>1 0<br>1 1 | 1<br>1<br>0<br>0 |

| (a                   | )                | (Ե                       | )                | 1 | (0                       | ]                |

clearer by

$$\frac{\partial f}{\partial A_j} = \frac{f(A_j = 1) \oplus f(A_j = 0)}{1 \oplus 0}$$

which is a Boolean variant of the ordinary derivative of a real function  $f(x_1, x_2, ..., x_n)$ :

$$\frac{\partial f}{\partial x_i} = \lim_{a \to 0} \frac{f(x_j = a) - f(x_j = 0)}{a - 0}$$

We apply the above to the example function f(A, B, C) of Table 1.4 by choosing  $A_j$  to be equal to A. The subfunctions f' and f'' are found by merely slicing Table 1.4 into two halves, yielding Table 1.6a and Table 1.6b, respectively. The subfunction f''' is subsequently constructed by XORing the columns f' and f'', yielding Table 1.6c.

#### 1.8

#### **Boolean Decompositions**

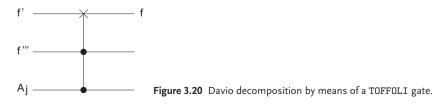

Subfunctions are particularly useful when implementing a Boolean function. Assume that we want to build a hardware circuit that realizes a function f of n variables. We have the following identities:

$$f = f' \overline{A_j} + f'' A_j$$

=  $f' \oplus f''' A_j$ . (1.3)

The former expression is called the Shannon decomposition (named after the American engineer Claude Shannon); the latter expression is known as the Davio decomposition (after the Belgian engineer Marc Davio).<sup>5</sup> As the subfunctions f',

5) We limit ourselves here to the so-called 'positive Davio decomposition'. We thus ignore the 'negative Davio decomposition'  $f'' \oplus f''' \overline{A_i}$ .

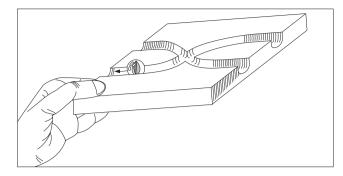

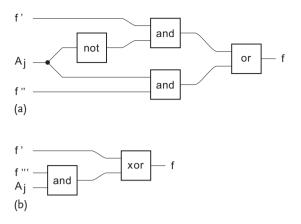

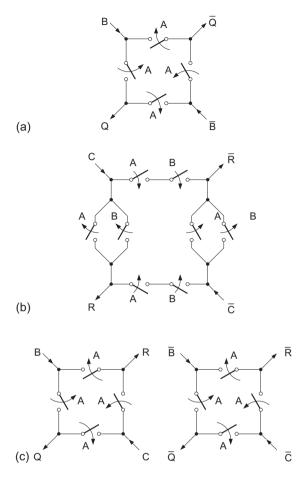

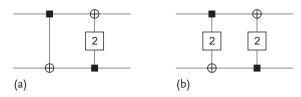

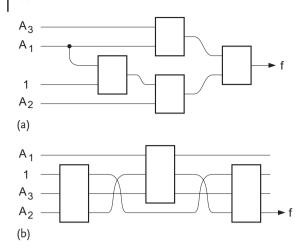

Figure 1.1 Circuit decompositions: (a) Shannon decomposition, (b) Davio decomposition.

Figure 1.2 Davio decomposition.

f'', and f''' are functions of only n - 1 variables, both identities allow us to reduce the original design problem to two smaller design problems. Applying such a decomposition over and over again (each time with another variable  $A_j$ ) eventually allows the synthesis problem to be reduced to trivial functions (i.e., literals or constants). Figure 1.1 shows the two circuit decompositions.

Figure 1.2 shows the result of applying the Davio decomposition to the example function (Table 1.4) twice: once with  $A_j = A$  (right side of the figure), and then with  $A_j = B$  (left side).

#### 1.9 Exercises for Chapter 1

#### Exercise 1.1

XOR and XAND are injective in the first argument; OR, NOR, AND, and NAND are noninjective in the first argument. Verify that the same properties hold in the second argument (why is this the case?).

#### Exercise 1.2

Which of the 16 functions f(A, B) is both injective in the first argument and non-injective in the second argument?

#### Exercise 1.3

Prove the second identity in (1.1). Demonstrate that, if *X* and *Y* represent different minterms, then this simplifies to

$$X + Y = X \oplus Y .$$

#### Exercise 1.4

Apply (1.1) in order to obtain (1.2).

#### Exercise 1.5

Verify the dual identities of (1.1):

$$\overline{X} = 0 \odot X$$

$$XY = X \odot Y \odot (X + Y)$$

#### Exercise 1.6

A Boolean function is said to be 'even' if it has an even number of 1s (and thus also an even number of 0s) in its truth table. Otherwise, it is said to be 'odd'. In other words, an even function has an even number of terms in its minterm expansion, while an odd function has an odd number of terms in its minterm expansion. Demonstrate the following properties:

- If both *f* and *g* are even, then  $f \oplus g$  is even.

- If both *f* and *g* are odd, then  $f \oplus g$  is even.

- If *f* is even and *g* is odd, then  $f \oplus g$  is odd.

## Exercise 1.7

Prove the property mentioned at the end of Section 1.3.3: that all balanced functions lack the highest-degree term  $A_1A_2...A_n$  in their Reed–Muller expansions. Demonstrate (with the help of a counterexample) that the inverse theorem (i.e., that all functions lacking the highest-degree Reed–Muller term are balanced) is false.

#### Exercise 1.8

Find the minterm expansion, the maxterm expansion, the Reed–Muller expansion, and the minimum ESOP expansions of the function  $f_2(A, B)$  of Table 1.2.

**Exercise 1.9** Check (1.3).

# 2 Group Theory

# 2.1 Introduction

One very important mathematical tool for investigating reversible circuits and computers is the group. For mathematicians, a group **G** is a combination of two things:

- A set  $S = \{a, b, c, ...\}$ , and

- An operation  $\Omega$  (involving two elements of the set).

However, the set and operation must fulfil four conditions. Applying the infix notation for the bivariate function  $\Omega$ , these conditions are:

- *S* must be closed:  $a\Omega b \in S$ .

- $\Omega$  must be associative:  $(a\Omega b)\Omega c = a\Omega(b\Omega c).$

- S must have an identity element *i*:

aΩ *i* = a.

- Each element of *S* must have an inverse in *S*:  $a\Omega a^{-1} = i$ .

The number of elements in the set is called the order of the group.

We start with an example. The set of all  $2^{2^n}$  Boolean functions of *n* variables (Section 1.3) forms a group with respect to the operation XOR (and thus with  $\Omega = XOR$ ). All four conditions are fulfilled:

- If  $f_1$  and  $f_2$  are Boolean functions, then  $f_1 \oplus f_2$  is too.

- If f<sub>1</sub>, f<sub>2</sub>, and f<sub>3</sub> are Boolean functions, then (f<sub>1</sub> ⊕ f<sub>2</sub>) ⊕ f<sub>3</sub> equals f<sub>1</sub> ⊕ (f<sub>2</sub> ⊕ f<sub>3</sub>). Therefore, we simply write f<sub>1</sub> ⊕ f<sub>2</sub> ⊕ f<sub>3</sub>.

- There is an identity element *i*: the zero function 0. Indeed, if *f* is an arbitrary function, then *f* ⊕ 0 = 0 ⊕ *f* = *f*.

- If *f* is an arbitrary function, *f* is its own inverse, as  $f \oplus f = 0$ .

18 2 Group Theory

A counterexample is obtained by combining the same set with the OR operation. We have:

- If  $f_1$  and  $f_2$  are Boolean functions, then  $f_1 + f_2$  is too.

- If  $f_1$ ,  $f_2$ , and  $f_3$  are Boolean functions, then  $(f_1 + f_2) + f_3$  equals  $f_1 + (f_2 + f_3)$ .

- There is an identity element i = 0. If f is an arbitrary function, then f + 0 =0 + f = f.

However, if *f* is an arbitrary function that is different from the zero function (and thus there is at least one 1 in the output column of the truth table), then there is no function g such that f + g = 0. Thus, the last group condition (existence of an inverse) is not fulfilled. This once again illustrates the fundamental difference between the XOR and NXOR operations on the one side, and the OR, NOR, AND, and NAND operations on the other hand.

We now give a second example of a group. The set *S* contains only two elements: the zero function 0 and one particular Boolean function *f* of *n* variables, with only one 1 in the truth table's output column. In other words, the minterm expansion of f consists of a single minterm. Therefore, we call it a minterm function. For a group, besides the set  $S = \{0, f\}$ , we also need a bivariate operation. The operation  $\Omega$  is again the XOR function. The reader is invited to verify that all group conditions are fulfilled, such as the first group condition (in other words, that  $0 \oplus 0$ ,  $0 \oplus f$ ,  $f \oplus 0$ , and  $f \oplus f$  are in  $\{0, f\}$ ). We may call the group a *minterm group*. The order of the group is 2. Mathematicians call this group the 'symmetric group of degree 2', which is denoted  $S_2$ . In general, the symmetric group of degree *n* consists of all possible permutations of *n* objects. It is denoted  $S_n$  and is of order *n*! (i.e., the factorial of *n*). This will occupy center stage in the present book.

Below, we will drop the explicit rendering of the symbol  $\Omega$  by writing *ab* instead of  $a\Omega b$ . We also will call ab the product of a and b, even in cases where  $\Omega$  is not a multiplication. Note that ab is often not the same as ba. Groups where ab =ba for all couples  $\{a, b\}$  are called *commutative* or Abelian groups (after the young Norwegian mathematician Niels Abel, pioneer of the theory of finite groups). Most of the groups we encounter in the present book are *not* Abelian. The group  $S_2$  is Abelian; the groups  $S_n$  with n > 2 are not Abelian.

Two groups, G and H, are said to be isomorphic if they have the same order and there is a one-to-one relationship  $g \leftrightarrow h$  between the elements g of **G** and the elements *h* of **H**, such that  $g_1 \leftrightarrow h_1$  and  $g_2 \leftrightarrow h_2$  automatically implies  $g_1g_2 \leftrightarrow h_2$  $h_1h_2$ . In other words, the two groups have the same 'product table' (or 'Cayley table', after the British mathematician Arthur Cayley).

We make a distinction between three kinds of groups according to group order. There are:

- Finite groups (i.e., groups with a finite order), and

- Groups of infinite order, where we must distinguish between

- Groups with a denumerable (or countable) infinity of elements, and

- Groups with a nondenumerable (or uncountable) infinity of elements.

Groups with a finite order or an order of denumerable infinity are called *discrete* groups. Uncountably infinite groups are known as Lie groups (named after another Norwegian mathematician, Sophus Lie, pioneer of the theory of infinite groups). The order of an infinite discrete group equals the cardinality of the natural numbers  $\mathbb{N} = \{0, 1, 2, ...\}$ , and will be denoted  $\aleph_0$ , the aleph-null convention introduced by the German mathematician Georg Cantor. The order of a Lie group equals the cardinality of the real numbers  $\mathbb{R}$ , and will be denoted either  $\infty$  or  $\infty^m$ , where *m* is the dimension of the group space.

The three kinds of groups behave quite differently. In the present book we will mainly focus on finite groups. We will only encounter infinite groups in Chapters 5 and 7. To learn more about finite groups in general and symmetric groups in particular, the reader is referred to appropriate textbooks [10-12]. For more on Lie groups, the reader can consult some other textbooks [13-15]. Books on denumerably infinite groups are rare. Some aspects of the subject are discussed by Kaplansky [16].

We end this section by giving two examples of an infinite group. The first example is a discrete group: the set S consists of all rational numbers of the form  $2^k$ (where k is an arbitrary integer number), so  $S = \{\dots, \frac{1}{4}, \frac{1}{2}, 1, 2, 4, 8, \dots\}$ , together with the operation of ordinary multiplication. This group is isomorphic to the infinite cyclic group **Z**. Its order is  $\aleph_0$ .

The second example is a Lie group: the set consists of all matrices of the form

$$\begin{pmatrix} 1 & 0 \\ 0 & \exp(i\theta) \end{pmatrix}$$

(where *i* is the imaginary unit and  $\theta$  is an arbitrary real number), together with the operation of matrix multiplication. This particular group is isomorphic to the Lie group U(1), i.e., the so-called unitary group of degree 1. Its order is  $\infty^1$ .

#### 2.2 **Permutation Groups**

The study of permutation groups is interesting because any finite group is isomorphic to some permutation group. A permutation group consists of a set of permutations together with the operation of cascading. Tables 2.1a and 2.1b show two different permutations of the eight objects 1, 2, 3, 4, 5, 6, 7, and 8. Table 2.1c gives the permutation resulting from the cascading of the previous two permutations. In order to deduce Table 2.1c from Tables 2.1a and 2.1b, we proceed as follows. The first row of Table 2.1a indicates that '1 is mapped to 2', whereas the second row of Table 2.1b shows that '2 is mapped to 3'. Together, this says that '1 is mapped to 3' (to be filled in) in the first row of Table 2.1c. We can equally well say that, according to Table 2.1a, '2 is the image of 1', whereas, according to Table 2.1b, '3 is the image of 2'. Taken together, these indicate that '3 is the image of the image of 1' (to be filled in) in the first row of Ta-

ble 2.1c. Proceeding in this manner for all eight rows of Table 2.1a yields the full Table 2.1c.

The correspondence table notation is usually considered too cumbersome for permutations, and is therefore replaced by the cycle notation. The latter consists of a product of disjoint cycles. An example of a cycle is (1,2,3), meaning that 1 is mapped to 2, 2 is mapped to 3, and 3 is mapped to 1. Table 2.1a is written as (1,2,3)(5,6), whereas Table 2.1b is written as (2,3)(4,8)(5,6), and Table 2.1c as (1,3)(4,8). Cascading is represented by a multiplication symbol, such as \*. Thus we have the equality:

$$(1,2,3)(5,6)*(2,3)(4,8)(5,6) = (1,3)(4,8)$$

. (2.1)

Permutations can also be represented by permutation matrices; that is, square matrices where all entries are either 0 or 1 and the entries on each line sum to 1. By definition, a line sum is either a row sum or a column sum. Permutations of *n* objects are represented by  $n \times n$  permutation matrices. For example, (2.1) can be rewritten as a matrix equation:

| (0 | 1  | 0 | 0 | 0 | 0 | 0 | 0) |   | (1 | 0 | 0 | 0 | 0 | 0 | 0 | 0) |   |

|----|----|---|---|---|---|---|----|---|----|---|---|---|---|---|---|----|---|

| 0  | 0  | 1 | 0 | 0 | 0 | 0 | 0  |   | 0  | 0 | 1 | 0 | 0 | 0 | 0 | 0  |   |

| 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0  |   | 0  | 1 | 0 | 0 | 0 | 0 | 0 | 0  |   |

| 0  | 0  | 0 | 1 | 0 | 0 | 0 | 0  |   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1  | _ |

| 0  |    | 0 | 0 | 0 | 1 | 0 | 0  |   | 0  | 0 | 0 | 0 | 0 | 1 | 0 | 0  | _ |

| 0  |    | 0 | 0 | 1 | 0 | 0 | 0  |   | 0  | 0 | 0 | 0 | 1 | 0 | 0 | 0  |   |

| 0  | 0  | 0 | 0 | 0 | 0 | 1 | 0  |   | 0  | 0 | 0 | 0 | 0 | 0 | 1 | 0  |   |

| (0 | 0  | 0 | 0 | 0 | 0 | 0 | 1) | / | 0  | 0 | 0 | 1 | 0 | 0 | 0 | 0) |   |

|    |    |   |   |   |   |   |    |   |    |   |   |   |   |   |   |    |   |

|    | (0 | 0 | 1 | 0 | 0 | 0 | 0  | 0 | \  |   |   |   |   |   |   |    |   |

|    | 0  | 1 | 0 | 0 | 0 | 0 | 0  | 0 |    |   |   |   |   |   |   |    |   |

|    | 1  | 0 | 0 | 0 | 0 | 0 | 0  | 0 |    |   |   |   |   |   |   |    |   |

|    | 0  | 0 | 0 | 0 | 0 | 0 | 0  | 1 |    |   |   |   |   |   |   |    |   |

|    | 0  | 0 | 0 | 0 | 1 | 0 | 0  | 0 | ·  |   |   |   |   |   |   |    |   |

|    | 0  | 0 | 0 | 0 | 0 | 1 | 0  | 0 |    |   |   |   |   |   |   |    |   |

|    | 0  | 0 | 0 | 0 | 0 | 0 | 1  | 0 |    |   |   |   |   |   |   |    |   |

|    | 0  | 0 | 0 | 1 | 0 | 0 | 0  | 0 | )  |   |   |   |   |   |   |    |   |

As an example of a permutation group, we consider the group of all permutations of three objects 1, 2, and 3. This is of order 3! = 6. Its six elements are the six permutations (), (1,2), (1,3), (2,3), (1,2,3), and (1,3,2). It is the symmetric group of degree 3, denoted **S**<sub>3</sub>. Note that the element () is the trivial permutation that maps each object to itself. In other words: no object is 'moved' by (). This element is the identity element *i* of the permutation group. Its matrix representation is a diagonal matrix, with 1s exclusively on the diagonal.

| A                                    | Р                                    |  | Α                                    | Р                                    |     | Α                                    | Р                                    |  |

|--------------------------------------|--------------------------------------|--|--------------------------------------|--------------------------------------|-----|--------------------------------------|--------------------------------------|--|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 2<br>3<br>1<br>4<br>6<br>5<br>7<br>8 |  | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 1<br>3<br>2<br>8<br>6<br>5<br>7<br>4 |     | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 3<br>2<br>1<br>8<br>5<br>6<br>7<br>4 |  |

| (a)                                  |                                      |  | . (1                                 | <b>)</b>                             | (c) |                                      |                                      |  |

Table 2.1 Correspondence tables for three permutations of eight objects.

# 2.3 Matrix Groups

The study of matrix groups is also of interest, because any finite group is isomorphic to some matrix group and many infinite groups too. A matrix group consists of a set of square matrices together with the operation of matrix multiplication. The reader is invited to check that the following six  $2 \times 2$  matrices form a group:

$$\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}, \begin{pmatrix} 1/2 & -\sqrt{3}/2 \\ -\sqrt{3}/2 & -1/2 \end{pmatrix}, \begin{pmatrix} 1/2 & \sqrt{3}/2 \\ \sqrt{3}/2 & -1/2 \end{pmatrix}, \begin{pmatrix} -1 & 0 \\ 0 & 1 \end{pmatrix}, \begin{pmatrix} -1/2 & -\sqrt{3}/2 \\ \sqrt{3}/2 & -1/2 \end{pmatrix}, \text{ and } \begin{pmatrix} -1/2 & \sqrt{3}/2 \\ -\sqrt{3}/2 & -1/2 \end{pmatrix}.$$

(2.2)

Surprisingly, this group is isomorphic to the group of the six  $3 \times 3$  permutation matrices of S<sub>3</sub>:

$$\begin{pmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{pmatrix}, \quad \begin{pmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 1 \end{pmatrix}, \quad \begin{pmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \end{pmatrix},$$

$$\begin{pmatrix} 1 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \end{pmatrix}, \quad \begin{pmatrix} 0 & 1 & 0 \\ 0 & 0 & 1 \\ 1 & 0 & 0 \end{pmatrix}, \quad \text{and} \quad \begin{pmatrix} 0 & 0 & 1 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \end{pmatrix}.$$

Any matrix group consists of merely invertible matrices (also known as nonsingular matrices). A singular matrix (i.e., a matrix that has a determinant of zero) has no inverse.

#### 2.4

#### **Group Generators**

Generators of a group consist of any subset {*a*, *b*, *c*,...} of the set *S* such that all the other elements of *S* can be written as one of the 'products' *aa*, *ab*, *ac*, ..., *ba*, ..., *aaa*, *aab*, ... Surprisingly, the whole permutation group  $S_n$  can be generated using only two (well-chosen) generators, such as the two permutations (1,2) and (1,2,3,...,n). For example, for the case n = 3, we have the two generators a = (1,2) and b = (1,2,3). All six members of  $S_3$  can be written as a product:

$$() = 1$$

(1,2) = a

(1,3) = a\*b

(2,3) = b\*a

(1,2,3) = b

(1,3,2) = b\*b

Such decomposition is not unique. We may for example, write () = a\*a and also (1,3,2) = a\*b\*a.

As a second example, we consider all minterm functions  $f_1$ ,  $f_2$ ,  $f_4$ , and  $f_8$  from Table 1.2, together with the operation XOR. These do not form a group, as the set is not closed. For example,  $f_1 \oplus f_2$  equals  $f_3$ , which is not in the set { $f_1$ ,  $f_2$ ,  $f_4$ ,  $f_8$ }. The four minterms generate the full group { $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,...,  $f_{15}$ }. In general, the  $2^n$  minterms of n variables, together with the operation XOR, generate the group of all  $2^{2^n}$  functions of n variables.

Generators of a group are interesting since they act as building blocks for constructing arbitrary elements of the group. With a small set of building blocks (often called the 'library'), we can construct a huge number of combinations. It is sufficient to recall here that all n! permutations can be built by successive applications of only two bricks: a = (1,2) and b = (1,2,3,...,n). However, choosing such a small library is not a clever approach, since it can lead to very long cascades when realizing a particular permutation. For example, the permutation of Table 2.1b (where n = 8) requires at least 23 blocks:

$$(2,3)(4,8)(5,6) = b^2 a b a b a b^2 a b a b a b^3 a b^3 a b$$

Therefore, it is often convenient to choose larger sets of generators, which guarantee shorter products. The challenge to the designer is to choose a clever generator set (i.e., not too small, but also not too large). A substantial part of the present book is devoted to this task. The task of the circuit designer is aided by the availability of dedicated computer algebra packages. Indeed, besides well-known computer algebra languages (such as Reduce, Maple, Mathematica, etc.), there are special-purpose languages that are dedicated to group theory. For finite groups, we should mention Magma [17, 18], Cayley [18, 19], and GAP [20]. For Lie groups, there is LiE [21, 22]. Many of the results given in this book were either discovered or verified by means of GAP.

#### 2.5 Subgroups

One important aspect of a group is its subgroups. For example, the two matrices

$$\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix} \quad \text{and} \quad \begin{pmatrix} -1 & 0 \\ 0 & 1 \end{pmatrix} =$$

which form a subset of the set (2.2), form a group of their own, isomorphic to  $S_2$ , the group of permutations of two objects. We say that this two-element group is a subgroup of the six-element group. We write:

$$S_2 \subset S_3$$

,

which we may read as either ' $S_2$  is a subgroup of  $S_3$ ' or ' $S_3$  is a supergroup of  $S_2$ '.

If  $\mathbf{G}$  is finite and a supergroup of  $\mathbf{H}$ , then the ratio

is called the index of H in G. Lagrange's theorem (named after the Italian/French mathematician/astronomer Joseph-Louis Lagrange) says that such an index is always an integer. In other words, the order of a subgroup divides the order of its supergroup. This theorem strongly restricts the number of subgroups of a given group. Nevertheless, most groups have a wealth of subgroups. For example, the group  $S_4$  (of order 4! = 24) has 30 different subgroups, whereas  $S_8$  (of order  $8! = 40\ 320$ ) has 151 221 subgroups [23].

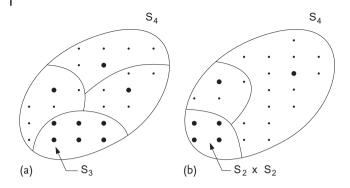

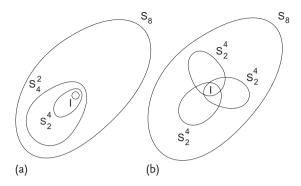

#### 2.6 Young Subgroups

Symmetric groups have a special class of subgroups, called *Young subgroups* (after the English priest/mathematician Alfred Young). These take advantage of the notion of the direct product of two groups. We introduce this product by giving an example of a Young subgroup of  $S_5$ . Assume that we have five objects a, b, c, d, and e. There are a total of 5! = 120 permutations of these objects. However, let us also impose a restriction: we will only allow permutations that permute a, b, and c among each other and (simultaneously) permute d and e among each other. This allows 3! permutations of three objects, while (independently) allowing 2! permutations of two objects. The allowed permutations form a permutation group of order  $3! \times 2! = 12$ . We are allowed to 'combine' each element of  $S_3$  with each element of  $S_2$ . Therefore, the group is called a *direct product* of  $S_3$  and  $S_2$ , denoted  $S_3 \times S_2$ . We write

${\boldsymbol{S}}_3\times{\boldsymbol{S}}_2\subset{\boldsymbol{S}}_5$  .

The subgroup is based on a particular partition of the number 5:

3 + 2 = 5.

In general, we may combine any group  $G_1$  with any group  $G_2, \ldots$ , with any group  $G_m$ . Of course, we have

$\operatorname{order}(\mathbf{G}_1 \times \mathbf{G}_2 \times \ldots \times \mathbf{G}_m) = \operatorname{order}(\mathbf{G}_1) \times \operatorname{order}(\mathbf{G}_2) \times \ldots \times \operatorname{order}(\mathbf{G}_m)$ .

As an example, we consider the group formed by the set of all  $2^{2^n}$  Boolean functions of *n* Boolean variables, together with the operation of XORing (see Sections 2.1 and 2.4). They form a group isomorphic to the direct product  $S_2 \times S_2 \times ... \times S_2$  with  $2^n$  factors, with order

$$\operatorname{order}(\mathbf{S}_2 \times \mathbf{S}_2 \times \ldots \times \mathbf{S}_2) = (\operatorname{order}(\mathbf{S}_2))^{2^n} = 2^{2^n}$$

Each factor  $S_2$  refers to what was called a minterm group in Section 2.1.

A Young subgroup [24–26] of the symmetric group  $S_n$  is defined as any subgroup that is isomorphic to  $S_{n_1} \times S_{n_2} \times \ldots \times S_{n_k}$ , with  $(n_1, n_2, \ldots, n_k)$  being a partition of the number n; that is, with

$n_1 + n_2 + \cdots + n_k = n \; .$

The order of this Young subgroup is  $n_1!n_2!\dots n_k!$ .

The number of different Young subgroups of the group  $S_n$  is given by the Bell number  $B_n$  (named after the Scottish/American mathematician Eric Bell). For example, the group  $S_4$  has  $B_4 = 15$  Young subgroups:

- One trivial subgroup isomorphic to **S**<sub>4</sub>,

- Three subgroups isomorphic to **S**<sub>2</sub> × **S**<sub>2</sub>,

- Four subgroups isomorphic to **S**<sub>1</sub> × **S**<sub>3</sub>,

- Six subgroups isomorphic to  $S_1 \times S_1 \times S_2$ , and

- One trivial subgroup isomorphic to  $S_1 \times S_1 \times S_1 \times S_1$ .

The group  $S_8$  has  $B_8 = 4140$  Young subgroups.

Because  $S_1$  is just the trivial group I with one element (i.e., the identity element *i*), Young subgroups of the form  $S_1 \times S_k$  are often simply denoted by  $S_k$ . Finally, Young subgroups of the form  $S_k \times S_k \times ... \times S_k$  (with *m* factors) will be written as  $S_{\nu}^m$ .

#### 2.7

#### Sylow p-Subgroups

Sylow *p*-subgroups, named after a third Norwegian group theorist, Ludwig Sylow, comprise another peculiar kind of subgroup. Let us assume an arbitrary (i.e., not necessarily symmetric) group **G**. Its order, *G* (just like any integer number larger than 1), can be written as a prime factorization:

$$G = 2^{x_2} 3^{x_3} 5^{x_5} \dots p^{x_p} \dots$$

where all of the exponents  $x_p$  are integers (either 0 or positive). In this case, any subgroup **H** of **G**, with an order *H* that satisfies

$$H = p^{x_p}$$

is called a Sylow *p*-subgroup of **G**.

## 2.8 Cyclic Subgroups

We now consider an arbitrary element g of an arbitrary but finite group **G**, as well as the sequence  $g, g^2, g^3, \ldots$  Because of the closeness property of the group (see Section 2.1), all of the powers  $g^j$  are members of the group **G**. In order to guarantee the finiteness of **G**, there must be an exponent n such that  $g^n$  equals the identity element i of **G**. Then,  $g^{n+1}$  is equal to g, whereas  $g^{n+2}$  is equal to  $g^2$ , etc., and there are only a finite number of different powers  $g^j$ . Thus, the infinite sequence  $\{g, g^2, g^3, \ldots\}$  is periodic with a period of n. We call n the order of the element g. The finite sequence  $\{g, g^2, g^3, \ldots, g^n\}$  forms a subgroup of **G** that is isomorphic to the group called the 'cyclic group of degree n' and denoted  $\mathbf{Z}_n$ . Because of Lagrange's theorem, any element g of **G** has an order that is a divisor of the group order.

The order of  $\mathbf{Z}_n$  is equal to *n*. We have

$\mathbf{Z}_n \subset \mathbf{S}_n$  ,

and, in particular,

$\mathbf{Z}_2 = \mathbf{S}_2 \ .$

All cyclic groups  $\mathbf{Z}_n$  are Abelian.

## 2.9 Closing Remarks

This book is strongly grounded in a group-theoretical approach. This may surprise some readers. Group theory is sometimes considered to be overkill when discussing reversible computing. However, it is my feeling that groups in reversible computing are not introduced, let alone invented. They are merely discovered. Indeed, they are inherently present, whether one likes it or not. Unearthing them has two benefits:

- We see reversible computing as an example of more general mathematical schemes, and

- We can benefit from the many theorems discovered and tools developed by group theorists.

We discussed some of these theorems and tools above. More of them will be useful when investigating reversible computers, such as cosets, double cosets, conjugated subgroups, ... In order to ensure that the present chapter is relatively brief, and to allow us to focus on the subject of this book (i.e., reversible computers) as quickly as possible, we will introduce these concepts later on, when we actually need them.

One final (practical) remark. In the sections above, we adopted some conventions regarding group notation. For instance, a finite group is denoted by a bold-faced capital; the order of a group is denoted by a capital; and an element of a group is denoted by a lower-case letter. For example:

$g \in \mathbf{G}$ order( $\mathbf{G}$ ) = G.

For the rest of this book, we will (whenever possible) respect this convention.

# 2.10 Exercises for Chapter 2

## Exercise 2.1

Prove that, in a group, we do not have to make any distinction between a 'right identity element' and a 'left identity element'. In other words, if  $i_1$  and  $i_2$  are two particular elements of a group, such that for all elements *a* of the group

both  $a\Omega i_1 = a$  and  $i_2\Omega a = a$ ,

then necessarily  $i_1 = i_2$ . This property also holds for non-Abelian groups!

#### Exercise 2.2

Prove that a group can only have one identity element. In other words, if  $i_1$  and  $i_2$  are two particular elements of a group, such that for all elements *a* of the group

both  $a\Omega i_1 = a$  and  $a\Omega i_2 = a$ ,

then necessarily  $i_1 = i_2$ .

#### Exercise 2.3

Prove that there is no distinction between 'right inverse' and 'left inverse'.

## Exercise 2.4

Prove that an element of a group can have only one inverse.

#### Exercise 2.5

In  $S_3$  (see Sections 2.2 and 2.3), what is the inverse of each of the six elements? In other words, what are ()<sup>-1</sup>, (1,2)<sup>-1</sup>, (1,3)<sup>-1</sup>, (2,3)<sup>-1</sup>, (1,2,3)<sup>-1</sup>, and (1,3,2)<sup>-1</sup>? Or: what are

$$\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}^{-1}, \quad \begin{pmatrix} 1/2 & -\sqrt{3}/2 \\ -\sqrt{3}/2 & -1/2 \end{pmatrix}^{-1}, \quad \begin{pmatrix} 1/2 & \sqrt{3}/2 \\ \sqrt{3}/2 & -1/2 \end{pmatrix}^{-1}, \\ \begin{pmatrix} -1 & 0 \\ 0 & 1 \end{pmatrix}^{-1}, \quad \begin{pmatrix} -1/2 & -\sqrt{3}/2 \\ \sqrt{3}/2 & -1/2 \end{pmatrix}^{-1}, \quad \text{and} \begin{pmatrix} -1/2 & \sqrt{3}/2 \\ -\sqrt{3}/2 & -1/2 \end{pmatrix}^{-1}$$

Or: what are

$$\begin{pmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{pmatrix}^{-1} , \quad \begin{pmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 1 \end{pmatrix}^{-1} , \quad \begin{pmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \end{pmatrix}^{-1} ,$$

$$\begin{pmatrix} 1 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \end{pmatrix}^{-1} , \quad \begin{pmatrix} 0 & 1 & 0 \\ 0 & 0 & 1 \\ 1 & 0 & 0 \end{pmatrix}^{-1} , \quad \text{and} \begin{pmatrix} 0 & 0 & 1 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \end{pmatrix}^{-1} ?$$

## Exercise 2.6

In  $S_3$ , what is the order of each of the six elements?

#### Exercise 2.7

A derangement is a permutation where no object is mapped to itself. In other words, all objects are 'moved'. Demonstrate that the derangements of *n* objects *do not* form a subgroup of the group  $S_n$ ; that is, the group of all the permutations of those *n* objects.

## Exercise 2.8

Demonstrate that  $S_3$  is not Abelian, but that  $Z_3$  is Abelian.

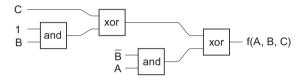

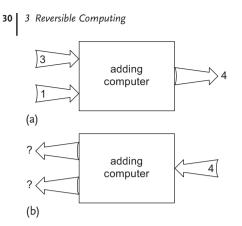

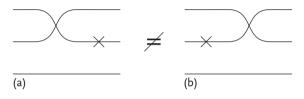

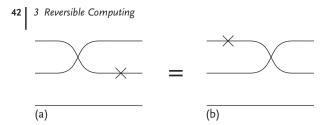

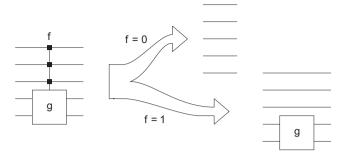

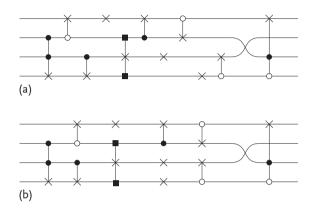

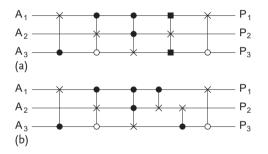

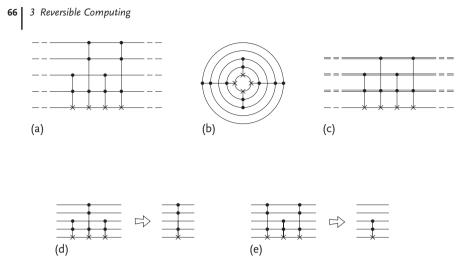

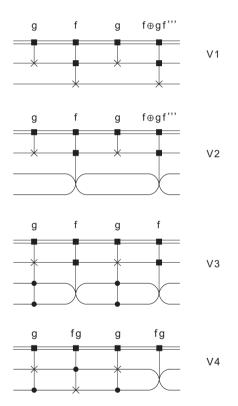

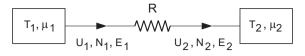

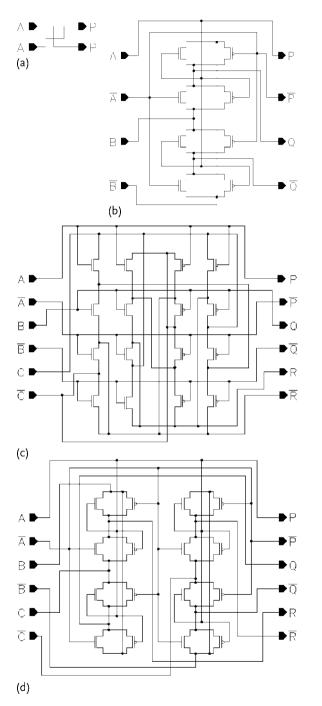

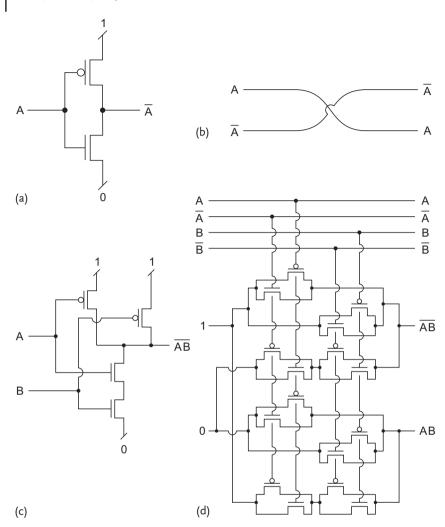

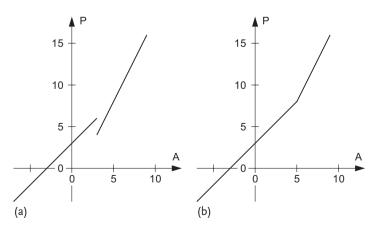

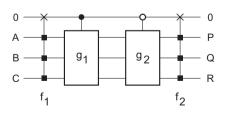

#### 3.1 Introduction

What is a reversible computer? Figure 3.1 explains by means of a counterexample. We see a small calculator that has been designed for one particular task: computing the sum of two numbers. This computation is logically irreversible because, if we forget the input values (i.e., 3 and 1), knowledge of the output value (i.e., 4) is not sufficient to recover the inputs, since 4 could equally well have been generated from 2 + 2 or 4 + 0 or 0 + 4 or ...

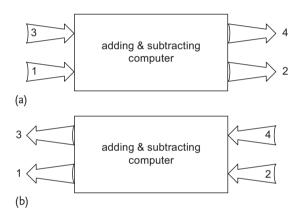

Figure 3.2 gives an actual example of a reversible computer. Again we have a pocket calculator, designed for a particular task: computing the sum of and the difference between two numbers. This computation is reversible because, if we forget the input values (3 and 1), knowledge of the output values (4 and 2) is sufficient to recover the inputs. If *A* and *B* designate the two input numbers and *P* and *Q* the two output numbers, then the knowledge that

$$P = A + B$$

$$Q = A - B \tag{3.1}$$

is sufficient to be able to work out that

$$A = \frac{1}{2}(P + Q)$$

$$B = \frac{1}{2}(P - Q) .$$

Thus, the outputs contain enough information to reconstruct the inputs. In other words: the outputs contain the same information as the inputs.

It is important to realize that all of the computers that are currently on the market are irreversible. Thus, to perform an experiment with a reversible computer, we must build such a machine ourselves. The building blocks of a digital computer are called digital circuits. The building blocks of a digital circuit are called logic gates. To build a reversible computer, the safest approach is to use only reversible building-blocks, and thus exclusively reversible logic gates. 29

Figure 3.1 A logically irreversible computer.

Figure 3.2 A logically reversible computer.

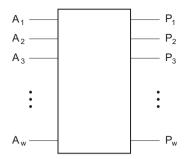

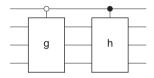

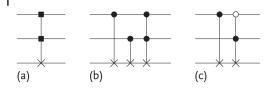

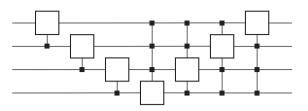

In the present chapter, we will demonstrate the application of group theory to the detailed design of reversible circuits from reversible gates. Such reversible logic gates are distinguished from conventional logic gates by two properties:

- The number of output bits always equals the number of input bits, and

- For each pair of different input words, the two corresponding output words are different.

For instance, it is clear that an AND gate (see the truth table in Table 1.3a) is not reversible, as

- It has two input bits but only one output bit, and

- For three different input words (i.e., for 00, 01, and 10), the three corresponding output words are equal.

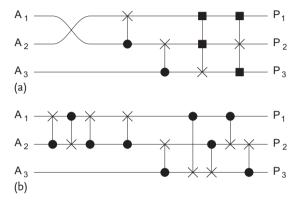

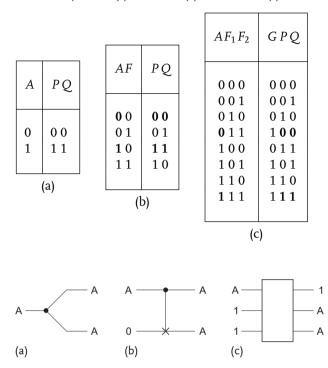

| AB                   | PQ                       |   | AB                       | PQ                       |   | AB                       | PQ                       |

|----------------------|--------------------------|---|--------------------------|--------------------------|---|--------------------------|--------------------------|

| 00<br>01<br>10<br>11 | 0 0<br>1 0<br>1 1<br>0 1 |   | 0 0<br>0 1<br>1 0<br>1 1 | 0 0<br>0 1<br>1 0<br>1 1 |   | 0 0<br>0 1<br>1 0<br>1 1 | 0 0<br>1 1<br>0 1<br>1 0 |

| (;                   | a)                       | 1 | (1                       | )                        | 1 | (0                       | c)                       |

| not =×               |                          |   |                          |                          |   |                          |                          |

Table 3.1 Truth tables of three reversible logic circuits of width 2: (a) an arbitrary reversible circuit r, (b) the identity gate i, and (c) the inverse  $r^{-1}$  of circuit r.

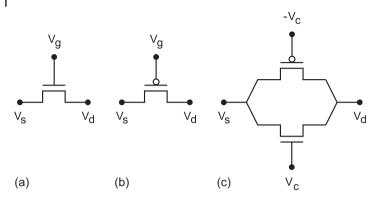

Figure 3.3 The NOT gate.

If, for example, we know that the output of the AND gate is 0, but we have forgotten the input values, knowledge of the output value is not sufficient to recover what the inputs have been. Indeed, 0 could equally well have been 0 AND 0 or 0 AND 1 or 1 AND 0. Analogously, neither the OR gate (Table 1.3b) nor the NAND gate nor the NOR gate are reversible.

In contrast, Table 1.1d is an example of a reversible gate: the NOT gate, also known as the *inverter*. This building-block is usually represented by a cross; see Figure 3.3. Table 3.1a gives another example of a reversible gate. Also here, the number of inputs equals the number of outputs (two). This number is called the width or logic width *w* of the reversible circuit *r*. The table gives all possible input words (A, B). We can see how all of the corresponding output words (P, Q) are different. Thus, the four (P, Q) words are merely a permutation of the four (A, B) words. This particular truth table may be replaced by a set of *w* Boolean equations:

$P(A, B) = A \oplus B$ O(A, B) = A.

This is equally well represented by the cycle notation (2,3,4) of the permutation of the four objects 1, 2, 3, and 4 (i.e., the four objects 00, 01, 10, and 11).

In contrast to arbitrary logic circuits, reversible logic circuits form a group. Remember that, for a group, we need a set (S) as well as an operation under which each pair (x, y) of elements of the set corresponds to a third element of the set (written xy). In our case, the operation applied to the two circuits is the cascading of the two circuits. Table 3.1b gives the truth table of the identity gate *i* (also known

as the *follower*), and Table 3.1c gives  $r^{-1}$ ; that is, the inverse of circuit *r*. The reader can easily verify that both the cascade  $rr^{-1}$  and the cascade  $r^{-1}r$  equal *i*.

Note that, in each of the truth tables of Table 3.1, the functions P(A, B) and Q(A, B) are both balanced. It is not difficult to prove the general property that, in a reversible truth table, all *w* functions  $P_j(A_1, A_2, ..., A_w)$  are balanced.<sup>6</sup> The restriction that all columns  $P_j$  are balanced is a necessary, though not sufficient, condition for reversibility.

# 3.2

### **Reversible Circuits**

All reversible circuits of the same width *w* (Figure 3.4) form a group. The truth table of an arbitrary reversible circuit has  $2^w$  rows. As all of the output words have to be different, they can merely be a repetition of the input words in a different order. In other words, the  $2^w$  output words are a permutation of the  $2^w$  input words. The  $(2^w)!$  permutations of  $2^w$  objects form the reversible group **R**, isomorphic to the symmetric group  $S_{2^w}$ . Thus there are exactly  $R(w) = (2^w)!$  different reversible logic circuits of width *w*. We recall here that the number  $2^w$  is called the degree of the group and the number  $(2^w)!$  is called the order of the group **R**. According to Section 2.3, each element of **R** can be represented by a  $2^w \times 2^w$  permutation matrix. For example, Table 3.1a is represented by the  $4 \times 4$  matrix

$$\begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \end{pmatrix} \ .$$

For small values of w, the order R of the group is given in Table 3.2. It is well known that the exponential function grows rapidly; it is also well known that the factorial function grows rapidly. It thus is no surprise that R(w), a factorial of an exponential, grows *very* rapidly. Stirling's asymptotic formula

$n! \approx \sqrt{2\pi} n^{n+1/2} e^{-n}$

(named after the Scottish mathematician James Stirling) is well known. The following inequalities [27]:

$$\sqrt{2\pi}n^{n+1/2}e^{-n} < n! < \sqrt{2\pi}n^{n+1/2}e^{-n}\left(1+\frac{1}{4n}\right)$$

contain somewhat more information. We use them to deduce an interval for the order of the symmetric group  $S_{2^w}$ :

$$2^{\left[w-\frac{1}{\log(2)}\right]2^{w}+\frac{w}{2}+1} < (2^{w})! < 2^{\left[w-\frac{1}{\log(2)}\right]2^{w}+\frac{w}{2}+2},$$

(3.2)

6) Besides using the notation *A*, *B*, *C*,... for the input bits and *P*, *Q*, *R*,... for the output bits, we will also use the letters *A*<sub>1</sub>, *A*<sub>2</sub>,..., *A*<sub>n</sub> for the inputs and *P*<sub>1</sub>, *P*<sub>2</sub>,..., *P*<sub>n</sub> for the outputs whenever this is more convenient. See also the footnote in Section 1.2.

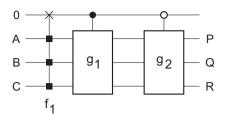

Figure 3.4 A circuit of logic width w.

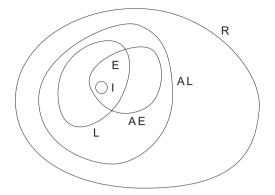

**Table 3.2** The number *R* of different reversible circuits, the number *C* of different conservative reversible circuits, the number *L* of different linear reversible circuits, the number *AL* of different affine linear reversible circuits, the number *E* of different exchanging circuits, and the number *AE* of different affine exchanging circuits, all as a function of the circuit width *w*.

| w | R                  | с       | L     | AL      | Ε  | AE  |

|---|--------------------|---------|-------|---------|----|-----|

| 1 | 2                  | 1       | 1     | 2       | 1  | 2   |

| 2 | 24                 | 2       | 6     | 24      | 2  | 8   |

| 3 | 40 320             | 36      | 168   | 1344    | 6  | 48  |

| 4 | 20 922 789 888 000 | 414 720 | 20160 | 322 560 | 24 | 384 |

|   |                    |         |       |         |    |     |

where 'log' stands for the natural logarithm. We note in passing that, in the prime factorization of the order; that is, in

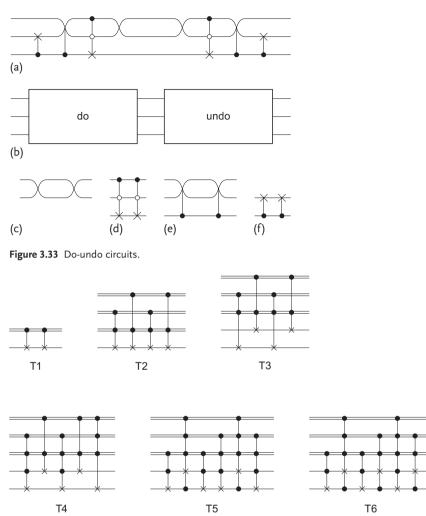

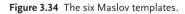

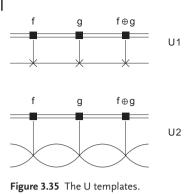

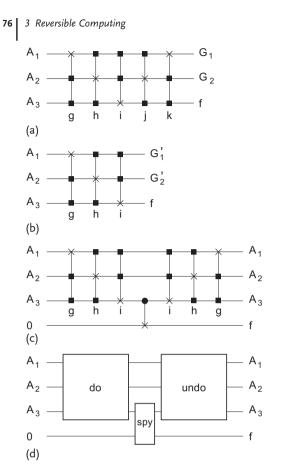

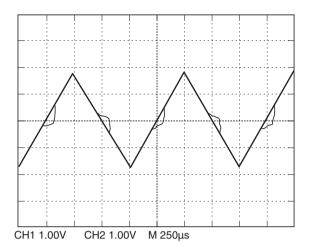

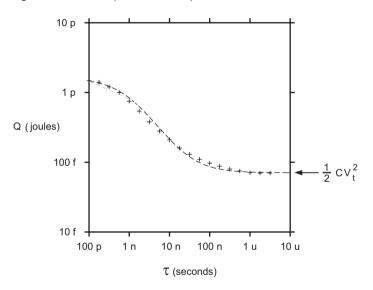

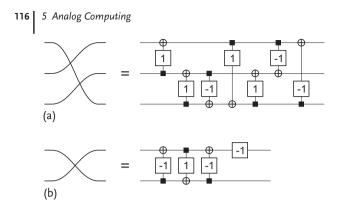

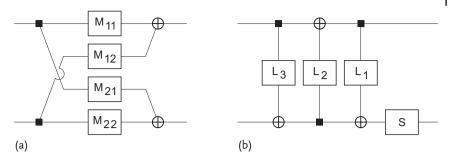

$$(2^{w})! = 2^{x_2} 3^{x_3} 5^{x_5} \dots$$

(3.3)

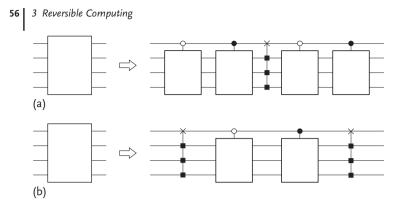

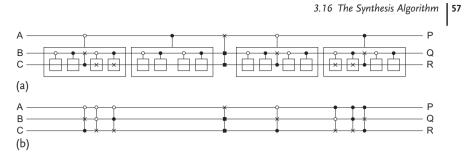

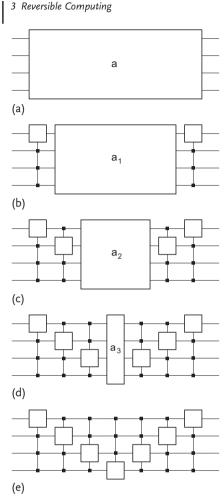

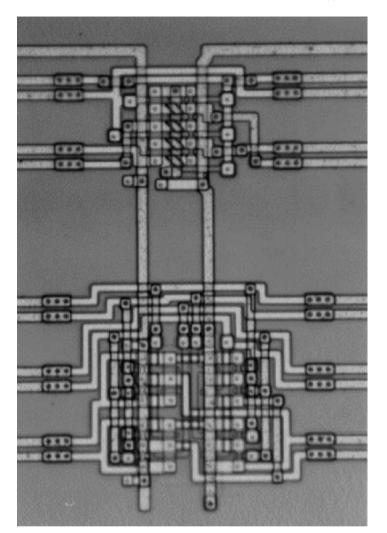

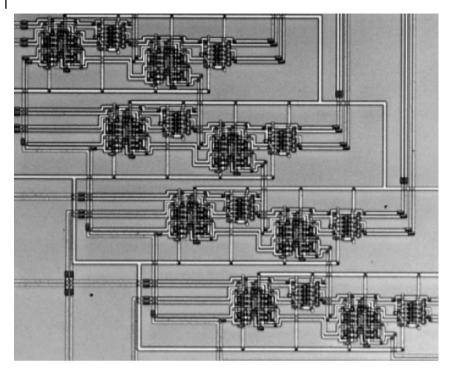

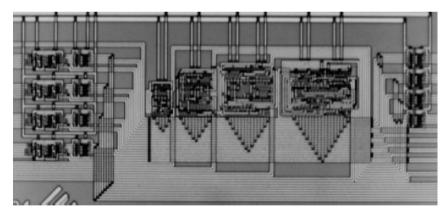

the exponent  $x_2$  of the prime factor 2 is easily computed: it equals the number of even factors in the factorial  $1 \times 2 \times 3 \times 4 \times \cdots \times (2^w - 1) \times 2^w$ , augmented by the number of quadruple factors in it, etc. Thus: